# Agilent W1160C Agilent Fault Detective

# **Getting Started Guide**

# Notices

© Agilent Technologies, Inc. 1996-2010

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Agilent Technologies, Inc. as governed by United States and international copyright laws.

#### **Edition**

Third Edition, January 2010

Printed in USA

Agilent Technologies, Inc. 3501 Stevens Creek Blvd. Santa Clara, CA 95052 USA

### **Trademark Information**

Adobe® is a trademark of Adobe Systems Incorporated.

Pentium<sup>®</sup> is a trademark of Intel Corporation in the U.S. and other countries.

Visual Studio<sup>®</sup> is a registered trademark of Microsoft Corporation in the United States and/or other countries.

Microsoft® is either a registered trademark or trademark of Microsoft Corporation in the United States and/or other countries.

Windows and MS Windows are U.S. registered trademarks of Microsoft Corporation.

Windows Vista® is either a registered trademark or trademark of Microsoft Corporation in the United States and/or other countries.

### **Software Revision**

This guide is valid for Revisions 4.x of the Fault Detective software, wherex refers to minor revisions of the software that do not affect the technical accuracy of this guide.

#### Warranty

The material contained in this document is provided "as is," and is subject to being changed, without notice, in future editions. Further, to the maximum extent permitted by applicable law, Agilent disclaims all warranties, either express or implied, with regard to this manual and any information contained herein, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein. Should Agilent and the user have a separate written agreement with warranty terms covering the material in this document that conflict with these terms, the warranty terms in the separate agreement shall control.

## **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

### **Restricted Rights Legend**

U.S. Government Restricted Rights. Software and technical data rights granted to the federal government include only those rights customarily provided to end user customers. Agilent provides this customary commercial license in Software and technical data pursuant to FAR 12.211 (Technical Data) and 12.212 (Computer Software) and, for the Department of Defense, DFARS 252.227-7015 (Technical Data - Commercial Items) and DFARS 227.7202-3 (Rights in Commercial Computer Software or Computer Software Documentation).

#### **Safety Notices**

## CAUTION

A **CAUTION** notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a **CAUTION** notice until the indicated conditions are fully understood and met.

## WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

#### **Introduction 7**

System Requirements 8 For Fault Detective Model Development 8 For the Fault Detective Runtime 9 Installing Fault Detective 10 Modifying or Repairing Fault Detective 10 Contacting Agilent 11 What is Agilent Fault Detective? 12 Modeling Overview 13

Components 14 Subcomponents 15 Functions 17 Tests 17

**Modeling Guidelines 19**

#### **The Fault Detective User Interface 21**

The Screen Layout 22 The Opening View 23 The Task Guide 24 The Components and Functions View 25 Adding Model Elements 26 Components and Functions Summary 26 Exploring Components, Subcomponents and Functions 27 Detail Panes 27

Viewing Coverage 29

Creating a Model Report 29

The Tests View 30

Adding Model Elements 31 Tests Summary 31 Exploring Tests 32 Creating a Model Report 32

The Predicted Performance View 33 Creating a Predicted Performance Report 34

The Suspect Faults View 35 Diagnosing a Syndrome 36 Creating a Suspect Faults Report 38

### **Digital Modeling Tutorial 39**

About This Tutorial... 40 Step 1. Create, Save, Close, and Re-Open the Model 42 Step 2. Add a Component 43 Step 3. Add More Components 46 Step 4. Add Subcomponents 49 Step 5. Add Bus Subcomponents 52 Step 6. Add Functions 55 Step 7. Begin Modeling Tests 59 Step 8. Add Coverage 63 Step 9. Verify the Model 65 Check for Unused Functions 65 Resolving Unused Functions 66 Check for Incomplete Tests 66 Resolving Incomplete Tests 67

Step 10. Use Predicted Performance to Improve the Model 69

Step 11. Add More Tests and Coverage 73 Step 12. Iteratively Improve the Model 76 Step 13. Create Reports 78 Where To Go Next 79

### **Diagnosing Suspect Faults 81**

About Diagnosing Suspect Faults... 82 How Fault Detective Diagnoses Suspect Faults 83 Diagnosis Example 84 Running the Diagnosis 85 Scoring Algorithms 88 What's in the Online Help? 89

### **Predicted Performance 91**

About Predicted Performance... 92 About Test Strategies... 92 Running the Predicted Performance Analysis 94 Using Analysis to Improve Test Coverage 97 Using Analysis to Optimize the Test Suite 101 What's in the Online Help? 106

#### **Modeling with Microsoft Excel 107**

Using Microsoft Excel with Fault Detective 108 Creating a New Model Using the Excel Template 109 Exporting a Model to Excel 111 Importing a Model from Excel 114 Entering and Editing Model Information in Excel 116

Export Options 120 One Test Group per Excel Worksheet 120 Multiple Test Groups per Excel Worksheet 122 What's in the Online Help? 123

### **Analog Modeling 125**

About the Analog Model... 126 Analog vs. Digital Modeling 128 Selecting Components 129 Use of Subcomponents 130 Identifying Functions 131 Typical Amplifier Functions 131 Typical Filter Functions 132 Typical Switch Functions 132 Typical Attenuator Functions 132 Typical Mixer Functions 132 Global Functions 134 Tests 136 Differentiating Faults 137

Testing Components to Different Specifications 138

## **Glossary 141**

Index 159

Agilent W1160C Fault Detective Getting Started Guide

# Introduction

1

System Requirements 8 Installing Fault Detective 10 What is Agilent Fault Detective? 12 Modeling Overview 13 Components 14 Subcomponents 15 Functions 17 Tests 17 Modeling Guidelines 19

This chapter contains installation information and an introduction to Fault Detective and modeling in Fault Detective.

# System Requirements

The system requirements for Agilent Fault Detective 4.7 are as follows:

## For Fault Detective Model Development

- Processor: minimum 2.0 GHz Pentium 4 or equivalent, Core 2 Duo recommended

- Operating system: One of the following 32-bit Microsoft Windows versions:

- Windows<sup>®</sup> 7 (32-bit systems only)

- Windows Vista<sup>®</sup> Enterprise (32-bit systems only)

- Windows XP Professional Service Pack 3 or later

- Windows Server 2008

- Windows Server 2003, Service Pack 1 or later

- Browser: Internet Explorer 6.0 or later is recommended

- Available memory: 1 GB or greater

- Available disk space:

- 225 MB required for installation (includes 160 MB for Microsoft .NET Framework)

- 175 MB required for operation (includes 110 MB for Microsoft .NET Framework)

- Video: XGA (1024x768) or better, 256 colors or more

- Optional: Microsoft Excel version 10 (commonly known as Excel 2002) or higher to export/import models to/from Excel

- You will need a copy of the free Adobe® Reader application to read the product manuals and other product literature in PDF format online. The Reader can be obtained at:

http://www.adobe.com

## For the Fault Detective Runtime

- Processor: minimum 2.0 GHz Pentium 4 or equivalent

- Operating system: One of the following 32-bit Microsoft Windows versions:

- Windows 7 (32-bit systems only)

- Windows Vista Enterprise (32-bit systems only)

- Windows XP Professional Service Pack 3 or later

- Windows Server 2008

- Windows Server 2003, Service Pack 1 or later

- Available memory: 1 GB or greater

- Available disk space:

- 225 MB required for installation (includes 160 MB for Microsoft .NET Framework)

- 175 MB required for operation (includes 110 MB for Microsoft .NET Framework)

# Installing Fault Detective

- **1** Close all other applications on your PC, insert the Fault Detective 4.7 CD into your CD-ROM drive, and follow the instructions on your screen.

- **3** Leave the **Run the Agilent Fault Detective License Activator** check box selected. Following the installation, follow the instructions to license your software. You will need the Order Number and Certificate Number from your Fault Detective License Entitlement Certificate.

| NOTE | If you are using floating (concurrent) licenses, do not use the Agilent      |

|------|------------------------------------------------------------------------------|

|      | Fault Detective License Activator. See the online help for directions: Click |

|      | Help > Contents and Index on the Fault Detective main menu; search for       |

|      | the help topic on Using Floating Licenses.                                   |

**4** If you have difficulty with the installation, contact Agilent as shown below.

## **Modifying or Repairing Fault Detective**

When you Repair or Modify Agilent Fault Detective, you may see a dialog with a message similar to the following:

The feature you are trying to use is on a CD-ROM or other removable disk that is not available.

#### Insert the 'Agilent Fault Detective 4.7' disk and click OK.

If you see this message, insert the Agilent Fault Detective CD into the CD-ROM drive of your PC. Windows will use the files on the CD to make repairs.

If you are using Windows Vista or Windows 7 with User Access Control (UAC) enabled, you may see this dialog box even if the CD is in the CD-ROM drive. You will be able to browse to the files on the CD, but you will get the dialog box above again and again when you click **OK**.

In order to complete the repair in this case, you must do one of the following two procedures:

- Perform the repair with User Access Control disabled:

- 1 Close the Windows Installer dialog box.

- **2** Disable User Access Control.

- **3** Restart the PC.

- **4** Perform the Repair or Modify operation.

- **5** Enable User Access Control and follow any further instructions from Windows. (You may be asked to restart your PC.)

- Run the installer from your desktop:

- **1** Do not close the Windows Installer dialog box shown above.

- **2** Copy the *Installer* folder from the Fault Detective CD to your PC's desktop.

- **3** Use the **Browse** button in the Windows Installer dialog box to browse to the location of the *Installer* folder on your desktop.

- 4 Select the installer file, *Agilent Fault Detective 4.7.msi*. Click **Open**.

## **Contacting Agilent**

In the United States, the primary contact center phone number is 1-800-829-4444.

To contact Agilent Technologies for technical and application assistance, consulting services, product selection and purchasing assistance, training and education, visit:

http://www.agilent.com/find/assist

# What is Agilent Fault Detective?

Agilent Fault Detective is a model-based software tool that diagnoses functional test failures, so repair and rework costs are greatly reduced. Given a set of functional test results, Fault Detective attempts to identify the faulty component or components based on a model of the test suite and the device under test (DUT).

Fault Detective can also perform analysis on your model and test suite by simulating defective components (faults) in your model, and by simulating the various patterns of test results (syndromes) that may be exhibited by these defective components. The results of this simulation are used to predict the detection and isolation performance of your test suite against the modeled DUT.

# **Modeling Overview**

Agilent Fault Detective uses a model to describe the interaction between a functional test suite and the device under test (DUT). When the functional test suite is applied to a DUT, each test returns a result of pass or fail. These functional test results, or a suitable subset of them, are then applied to the Fault Detective model for the DUT to produce the diagnosis.

The model is a means of capturing what you already know about how your tests verify your DUT–which components, buses, operations and characteristics are used by each test.

Within Fault Detective, you create a model which is a functional representation of your DUT and the tests performed on the DUT. This functional representation consists of components, subcomponents, functions and tests.

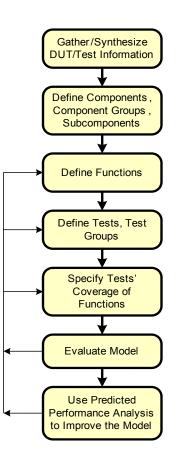

Figure 1 summarizes the Fault Detective modeling process.

#### 1 Introduction

## Components

Components represent the functionality provided by the DUT's physical parts. Often, several physical parts will be treated as a single component because they work together to provide a specific function and cannot be separated. In some cases, a physical part and a component will map to each other directly.

A component is an abstraction of the physical parts of the DUT. A component represents a structural element of a DUT performing one or more related functions. A component may be:

- Many physical parts—This is commonly used when a DUT has many discrete parts (for example, a power supply section), or when a test uses a function to exercise several indistinguishable physical parts.

- A single physical part–This is commonly used when the DUT has large complex parts (like ASICs).

- A block of parts.

- An entire assembly of parts-This is used when the component represents a complete printed circuit board.

## Subcomponents

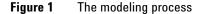

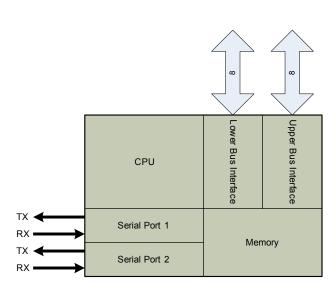

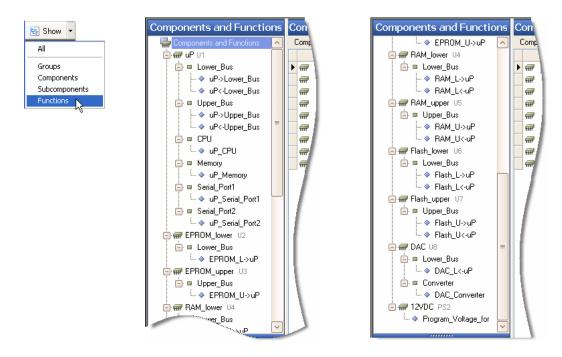

■ Subcomponents are logical subsets of a component. For example, a microprocessor chip could contain a CPU, memory, bus interface, and serial I/O elements. If these elements are tested in different functional tests (as they typically are), then model a component for the microprocessor chip and a subcomponent for each of these distinct elements. This finer level of granularity lets you define test usage for each subcomponent, giving you a higher degree of accuracy in your Fault Detective results.

Using subcomponents is highly encouraged and typically results in more accurate models. Since adding subcomponents adds to the complexity of the model, you can apply these more specific rules:

- A subcomponent represents a structural element of a component performing one or more related functions. Subcomponents are used to model DUT features such as:

- · A bus with associated read and write functions

- A signal group with associated functions such as "output enable", "output disable"

- A CPU with very separate functional blocks such as "floating point section" and "graphics section"

- For reasoning purposes, Fault Detective regards subcomponents as separate possible explanations for the failed tests. If one subcomponent works (for example, bus1), this does not imply that another subcomponent of the same component is working (for example, bus2).

You should use subcomponents if:

- The parent component represents a complex part (or perhaps a combination of several complex parts).

- The component can be broken into logical subcomponents.

- Small combinations of subcomponents are tested in different tests.

## **Functions**

Functions are attributes, characteristics, or behaviors of components or subcomponents.

From a digital standpoint, functions are often operations performed by the component. For example, a bus transceiver will typically have read and write functions.

From an analog standpoint, functions are often characteristics of the component or a set of components. For example, a filter will typically have flatness and insertion loss characteristics that can be modeled as functions.

## Tests

A test can be defined as one or more measurements or observations on a DUT that are evaluated to return information about the operational state of that DUT. A functional test suite is a set of functional tests that are run to determine whether a DUT is fully functional. Functional tests generally make one or more measurements on the DUT, and then pass judgment about some piece of functionality of the DUT. The result is pass or fail. If a test passes, it indicates a particular aspect of the DUT has been shown to be functional; if it fails, it indicates some portion of the functionality of one or more components isn't working.

In Fault Detective, you can model each functional test that can return a pass or fail judgment about some portion of the functionality of the DUT. In most cases, every test in a functional test suite should have a corresponding test element in the Fault Detective model. If there are tests in the test suite that do not evaluate the functionality of the DUT, you do not need to enter these tests into the Fault Detective model.

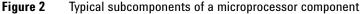

As shown below, tests use functions and functions exercise components/subcomponents.

## 1 Introduction

Figure 3 Tests use functions and functions exercise components/subcomponents

# **Modeling Guidelines**

- Create the model incrementally. Start small, enter syndromes, run analysis, make diagnoses, gain confidence, and add more model elements later. Your results will improve as you add detail to the model.

- Carefully name your model elements, especially functions. You do not want to have to remember the content of every function or open them to understand what they do. The name should imply the content clearly.

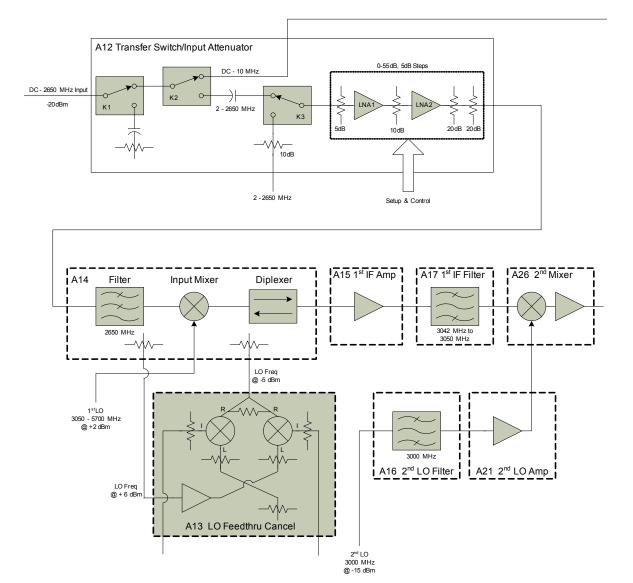

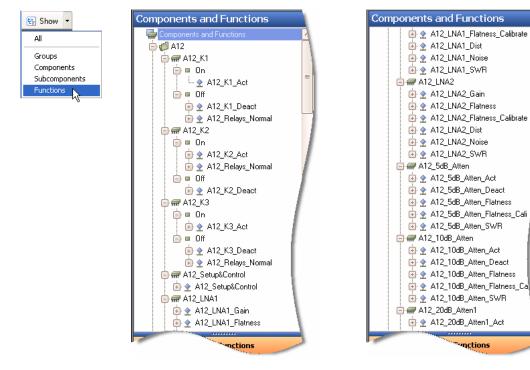

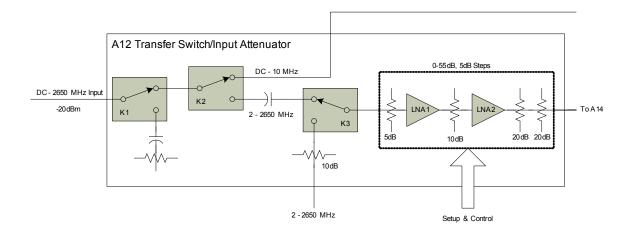

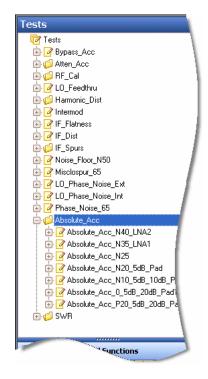

- Mark up a block diagram and enter only the components needed for a model. Do not enter the DUT's net list, bill of materials, or schematics directly. Typically, you will not need all that information. Select a section of the DUT and an interesting subset of tests. Group parts into logical blocks to hide unnecessary detail. For example, you can model a complex RF device at the amplifier, filter, and mixer level.

- Model at the logical level, not physical level. Do not model individual data and control lines. Instead, bundle them together into logical groups-for example, buses.

- Enter your selected components first with obvious subcomponents like buses and major control signals. These are the things that you probably already know will be important in describing test paths.

- For each component/subcomponent, enter obvious functions. Buses will almost always have read and write functions. Passive elements typically have only one function. Complex amplifiers will likely have several functions.

- Always model the tests and DUT the way they are and leave the diagnoses to Fault Detective. Do not try to model to force some perceived correct answer.

## 1 Introduction

Agilent W1160C Fault Detective Getting Started Guide

# The Fault Detective User Interface

The Screen Layout 22 The Opening View 23 The Components and Functions View 25 The Tests View 30 The Predicted Performance View 33 The Suspect Faults View 35

This chapter contains an overview of the Fault Detective user interface.

#### 2 The Fault Detective User Interface

# **The Screen Layout**

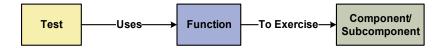

The screen layout, used throughout the application, consists of menus and toolbars, an explorer pane, a detail pane, navigation buttons, and a Task Guide.

Figure 4 The Fault Detective user interface

# **The Opening View**

Double-click the Fault Detective shortcut on your desktop to open the application. The opening view shows the menus, the standard toolbar, the status bar, and the Task Guide. The Fault Detective online help describes the menus, toolbars and status bar in detail. At any time, you can press the F1 key to get help on the current window.

| 🔯 Agilent Fault Detective            |                                                |

|--------------------------------------|------------------------------------------------|

| File Edit View Go Tools Actions Help |                                                |

| 👰 New 🔹 🚵 • 🖬 🖆 🐁 🐂 🖷 🗮 🗶 🏛 🛡        |                                                |

|                                      | Task Guide 🛛 🗙 🗙                               |

|                                      | Getting Started                                |

|                                      | Create a new model                             |

|                                      | 👌 Open a model                                 |

|                                      | 👶 Import a model from Excel                    |

|                                      | Sample Models                                  |

|                                      | 👰 View a sample model                          |

|                                      | How Do I                                       |

|                                      | Find more help on Agilent Fault     Detective? |

|                                      | More Information                               |

|                                      | (j) Getting started with Fault Detective       |

|                                      | (j) Best practices                             |

|                                      | (j) Modeling process overview                  |

| Ready                                |                                                |

## The Task Guide

The Task Guide is located on the right side of the screen and is particularly useful for new Fault Detective users. The information in the Task Guide changes as you move through the various views and provides shortcuts to operations, features and information. For example, in the Opening view, the Task Guide contains this information:

**Getting Started** Create a new model, Open a model, or Import a model from Excel.

**Sample Models** Choose from a model of an analog device or a digital device. These models are used in this getting started guide and show modeling fundamentals.

$\ensuremath{\text{How}}\xspace Do \ensuremath{I}\xspace ...$  Tasks associated with the current view appear here.

More Information Contains links to related information.

**Next and Previous Steps** As you move through the recommended model development steps, this icon in the Task Guide points the way to the next logical task step. Click this icon in the backtrack to the previous step in the process.

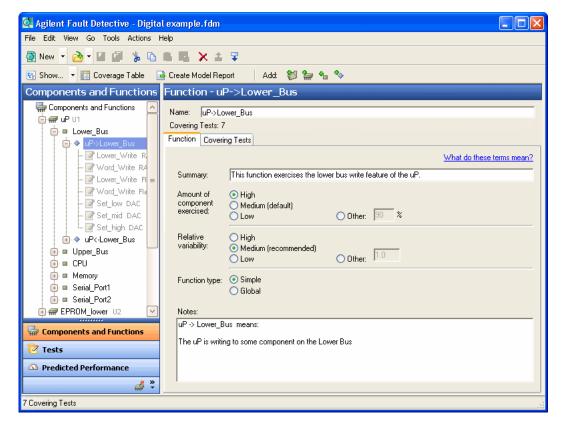

# **—** The Components and Functions View

🚔 Components and Functions

The Components and Functions view appears after you create a new model, open an existing model, or import model information from Excel. This view is where you add, delete, and edit component groups, components, subcomponents, and functions. You can access this view at any time by clicking the **Components and Functions** button.

| Agilent Fault Detective - Digita<br>File Edit View Go Tools Actions |           | ple.fdm            |                  |               |            | -          |                                                    |

|---------------------------------------------------------------------|-----------|--------------------|------------------|---------------|------------|------------|----------------------------------------------------|

| 👰 New - 🎅 📲 🖆 🐁 🖿                                                   |           |                    |                  |               |            |            |                                                    |

|                                                                     |           |                    |                  |               |            |            |                                                    |

| 🔄 Show 💌 🔝 Coverage Table 🛛                                         | 👌 Creati  | e Model Report     | Add:             | 10 <b>h</b> 1 | • *• · · · |            |                                                    |

| Components and Functions                                            | Com       | ponents and        | l Functio        | ns            |            |            | Task Guide 🛛 🗙 🗙                                   |

| Gomponents and Functions                                            | Comp      | ionents: 9         |                  |               |            |            | Previous step: Getting Started                     |

| 🕂 🛲 uP U1                                                           |           | Name               | Туре             | Subcom        | Functions  | Unused Pro | S Trevious step: detting started                   |

| 🔁 🛲 EPROM_lower U2                                                  | • 🛲       | uP                 | Compon           | 6             | 8          | 0          | (j) Fault Detective task steps                     |

| 🕂 🛲 EPROM_upper U3                                                  |           | EPROM_lower        | Compon           | 1             | 1          | 0          | Model Components and Durations                     |

| 🕂 🛲 RAM_lower U4                                                    |           | EPROM_upper        | Compon           | 1             | 1          | 0          | Model Components and Functions                     |

| 😥 🛲 RAM_upper US                                                    |           | RAM_lower          | Compon           |               | 2          | 0          |                                                    |

| 🔃 🛲 Flash_lower U6                                                  |           | RAM_upper          | Compon           |               | 2          | 0          | 🔛 Add a component                                  |

| 🔃 🛲 Flash_upper U7                                                  |           | Flash_lower        | Compon           |               | 2          | 0          | Add a component group                              |

|                                                                     |           | Flash_upper<br>DAC | Compon<br>Compon | -             | 2          | 0          | -                                                  |

| E HI 1200C F32                                                      |           | 12VDC              | Compon           |               | 1          | 0          | Edit coverage                                      |

|                                                                     |           | 12400              | Comport          | 0             | 1          | Ŭ          | Next step: Model tests                             |

|                                                                     |           |                    |                  |               |            |            | How Do I                                           |

|                                                                     |           |                    |                  |               |            |            | (2) Add coverage?                                  |

|                                                                     |           |                    |                  |               |            |            |                                                    |

|                                                                     |           |                    |                  |               |            |            | Compare components,<br>subcomponents or functions? |

| Gomponents and Functions                                            |           |                    |                  |               |            |            | More Information                                   |

| 🕜 Tests                                                             |           |                    |                  |               |            |            |                                                    |

| Predicted Performance                                               |           |                    |                  |               |            |            | (j) Modeling process overview                      |

| 4 ÷                                                                 |           |                    | 9 Comp           | 14 Subc       | 21 Func    | 0 Unuse    | (j) Advanced modeling techniques                   |

| B Components 14 Subcomponents                                       | 21 Functi | ons                |                  |               |            |            |                                                    |

Figure 6 The Digital example.fdm model shown in the Components and Functions view

# **Adding Model Elements**

You can use the **Add:** buttons in the toolbar or links in the Task Guide to add component groups, components, subcomponents and functions.

## **Components and Functions Summary**

Selecting the top level in the explorer pane shows a summary of the components and functions in the model.

| Components and Functions | С | Components and Functions |             |           |               |           |              |          |  |

|--------------------------|---|--------------------------|-------------|-----------|---------------|-----------|--------------|----------|--|

| Components and Functions |   | Components: 9            |             |           |               |           |              |          |  |

| 庄 🛲 uP U1                |   |                          | Name        | Туре      | Subcomponents | Functions | Unused Funct | Problems |  |

| 🐑 🛲 EPROM_lower U2       | Þ |                          | uP          | Component | 6             | 8         | 0            | 0        |  |

| 🔁 🛲 EPROM_upper U3       |   |                          | EPROM_lower | Component | 1             | 1         | 0            | 0        |  |

| 🔄 🛲 RAM_lower U4         |   | <b>#</b>                 | EPROM_upper | Component | 1             | 1         | 0            | 0        |  |

| 🔁 🛲 RAM_upper US         |   |                          | RAM_lower   | Component | 1             | 2         | 0            | 0        |  |

| 庄 🛲 Flash_lower U6       |   | <b>~</b>                 | RAM_upper   | Component | 1             | 2         | 0            | 0        |  |

| 😟 🛲 Flash_upper U7       |   | <b>~</b>                 | Flash_lower | Component | 1             | 2         | 0            | 0        |  |

| 庄 🛲 DAC U8               |   | <b>~</b>                 | Flash_upper | Component | 1             | 2         | 0            | 0        |  |

| 庄 🛲 12VDC PS2            |   | <b>~</b>                 | DAC         | Component | 2             | 2         | 0            | 0        |  |

|                          |   | <b>#</b>                 | 12VDC       | Component | 0             | 1         | 0            | 0        |  |

|                          |   |                          |             |           |               |           |              |          |  |

|                          |   |                          |             |           |               |           |              |          |  |

|                          |   |                          |             |           |               |           |              |          |  |

Figure 7 A summary of the components and functions in the *Digital example.fdm* model

## **Exploring Components, Subcomponents and Functions**

Expanding the tree in the explorer pane shows the underlying structure of your model. This hierarchical view shows component groups, components, subcomponents and functions. Click on any of these model elements to see more information in the detail pane.

| Generation and Functions | 1 | lame:                   | uP           |              |           |                        |          |  |

|--------------------------|---|-------------------------|--------------|--------------|-----------|------------------------|----------|--|

| 📄 🐖 uP U1                |   | Subco                   | mponents: 6  |              |           |                        |          |  |

| 🛞 💷 Lower_Bus            | _ | Component Subcomponents |              |              |           |                        |          |  |

| 😥 💷 Upper_Bus            |   | ompu                    |              | T            | E         | University Transferrer | Duchlass |  |

| 🕀 💷 CPU                  |   |                         | Name         | Туре         | Functions | Unused Functions       | Problems |  |

| 😥 💷 Memory               |   |                         | Lower_Bus    | Subcomponent | 2         | 0                      | 0        |  |

| 主 💷 Serial_Port1         |   |                         | Upper_Bus    | Subcomponent | 2         | 0                      | 0        |  |

| 吏 💷 Serial_Port2         |   |                         | CPU          | Subcomponent | 1         | 0                      | 0        |  |

| 🗄 🛲 EPROM_lower U2       |   |                         | Memory       | Subcomponent | 1         | 0                      | 0        |  |

| 🗄 🛲 EPROM_upper U3       |   |                         | Serial_Port1 | Subcomponent | 1         | 0                      | 0        |  |

| 🗄 🛲 RAM_lower U4         |   |                         | Serial_Port2 | Subcomponent | 1         | 0                      | 0        |  |

| 🗄 🛲 RAM_upper U5         |   |                         |              |              |           |                        |          |  |

| Flash_lower_             |   |                         |              |              |           |                        |          |  |

Figure 8 Click an item in the explorer pane to see more information in the detail pane

# **Detail Panes**

Selecting a function in the explorer pane exposes detail regarding the function and how it exercises the component/subcomponent.

Notice the Notes: area near the bottom in Figure 9. You can describe the function details here or add links to supporting documentation such as HTML files and URLs. This is an important Fault Detective feature allowing you to provide a transfer of knowledge from the model designer to the production floor. When necessary, test personnel can locate supporting documents such as schematics, block diagrams or parts cost information. The Notes: field is available for components, functions and tests.

Figure 9 Detail pane showing the *uP->Lower\_Bus* function

## **Viewing Coverage**

Click the **Covering Tests** tab for any function and get a listing of the test(s) using this function (an x in the Used column indicates the test(s) using this function).

| Components and Functions                          | Function - uP->                                                | Lower_Bus                  |      |                        |

|---------------------------------------------------|----------------------------------------------------------------|----------------------------|------|------------------------|

| Components and Functions                          | Name: uP->Lower_l<br>Covering Tests: 7<br>Function Covering Te |                            |      |                        |

| Lower_Write R.<br>Word_Write RA<br>Lower_Write FI | Show: All tests                                                | •                          | •    | How do I add coverage? |

| 📝 Word_Write Fla                                  | Test Information<br>Group N                                    |                            | Used | <u> </u>               |

| ··· 🕜 Set_low DAC<br>··· 🕜 Set_mid DAC            | Flash W                                                        | Word_Read                  |      |                        |

| Set_high DAC                                      |                                                                | .ower_Write<br>Jpper_Write | ×    |                        |

|                                                   |                                                                | Word_Write                 | x    |                        |

| ⊕ ■ CPU                                           |                                                                | Set_low                    | x    |                        |

| 🛨 💷 Memory                                        |                                                                | Set_mid                    | x    |                        |

|                                                   | 5                                                              | 5et_high<br>Read low       | ×    |                        |

|                                                   |                                                                | Read_mid                   |      |                        |

| 🖙 Components and Functions                        |                                                                | Read_high                  |      |                        |

| To-                                               | τ                                                              | εγ                         |      |                        |

Figure 10 Tests covering this function

## **Creating a Model Report**

Click the **Create Model Report** button on the toolbar to create an HTML report for the model. Refer to the Fault Detective online help for details regarding this report.

#### 2 The Fault Detective User Interface

# 🞯 The Tests View

🖉 Tests

Click the **Tests** button on the bottom left side of the screen to open the Tests view. The Tests view is where you add, delete or modify test groups and tests. Test groups and tests are listed hierarchically in the left explorer pane. Details for the selected test group or test are shown in the detail pane. The Task Guide shows test-related actions and shortcuts to supporting information.

| Agilent Fault Detective - Digita<br>File Edit View Go Tools Actions I |                     |            |          |         |          |                                                                                            |

|-----------------------------------------------------------------------|---------------------|------------|----------|---------|----------|--------------------------------------------------------------------------------------------|

| 👰 New 🔹 🚵 - 🔳 🗿 🐁 🐚                                                   | ● ■ × ± ▼           |            |          |         |          |                                                                                            |

| 🐑 Show 🔻 📑 Coverage Table 🔒                                           | Create Model Report | Add: 👸 👸   | ?        |         |          |                                                                                            |

| Tests                                                                 | Tests               |            |          |         |          | Task Guide 🛛 🗙                                                                             |

| Tests                                                                 | Groups: 7 Tests: 1  |            |          |         |          | O Previous step: Model components                                                          |

| 🗄 📝 CPU_Verify                                                        | Name                | Туре       | Tests    | Incompl | Problems | and functions                                                                              |

| 🔄 🧔 CPU_Int_RAM                                                       | CPU_Verify          | Test       | 1        | 0       | 0        | (i) Fault Detective task steps                                                             |

| 🔃 🃁 EPROM                                                             | CPU_Int_RAM         | Test Group | 4        | 0       | 0        |                                                                                            |

| 🔁 🃁 BAM                                                               | EPROM               | Test Group | 3        | 0       | 0        | Model Tests                                                                                |

| 🔃 🃁 Flash                                                             | 🗾 💋 RAM             | Test Group | 6        | 0       | 0        |                                                                                            |

| 🔁 📁 DAC                                                               | 📃 🧔 Flash           | Test Group | 6        | 0       | 0        | 🔁 Add a test                                                                               |

| 🔃 🥵 Serial_Port1                                                      | DAC 🧔               | Test Group | 6        | 0       | 0        | A                                                                                          |

| 🔃 🃁 Serial_Port2                                                      | 🧧 💋 Serial_Port1    | Test Group | 2        | 0       | 0        | 搅 Add a test group                                                                         |

|                                                                       | 🧾 💋 Serial_Port2    | Test Group | 2        | 0       | 0        | Edit coverage                                                                              |

|                                                                       |                     |            |          |         |          | Uiew test suggestions                                                                      |

|                                                                       |                     |            |          |         |          | Evaluate the structure of the model                                                        |

|                                                                       |                     |            |          |         |          | <ul> <li>Next step: Use predicted<br/>performance data to improve the<br/>model</li> </ul> |

| Components and Functions                                              |                     |            |          |         |          | How Do I                                                                                   |

| Tests                                                                 |                     |            |          |         |          | Ø Add coverage?                                                                            |

| Predicted Performance                                                 |                     |            |          |         |          | Ompare tests?                                                                              |

| 🝰 Suspect Faults                                                      |                     |            |          |         |          | More Information                                                                           |

| *                                                                     |                     | 8 Elements | 30 Tests | 0 Incom | 0 Proble |                                                                                            |

| 30 Tests                                                              |                     |            |          |         |          |                                                                                            |

Figure 11 The Digital example.fdm model shown in the Tests view

## **Adding Model Elements**

You can use the **Add:** buttons in the toolbar or links in the Task Guide to add test groups and tests.

## **Tests Summary**

Selecting the top level in the explorer pane shows a summary of the test groups and tests in the model. This allows you to easily locate any incomplete tests or problems relating to tests.

| ests             | Tests        |         |            |       |                  |          |

|------------------|--------------|---------|------------|-------|------------------|----------|

| 🕜 Tests          | Groups: 7 Te | ests: 1 |            |       |                  |          |

| 🛓 📝 CPU_Verify   | Name         |         | Туре       | Tests | Incomplete Tests | Problems |

| 😟 🃁 CPU_Int_RAM  | 🕨 📝 CPU_V    | /erify  | Test       | 1     | 0                | 0        |

| 🔃 🧔 EPROM        | 🛛 🧔 CPU_I    | int_RAM | Test Group | 4     | 0                | 0        |

| 🖻 🃁 BAM          | 🛑 🧔 EPROI    | м       | Test Group | 3     | 0                | 0        |

| 😟 🃁 Flash        | 📕 🧔 RAM      |         | Test Group | 6     | 0                | 0        |

| 🖶 խ DAC          | 📕 🧔 Flash    |         | Test Group | 6     | 0                | 0        |

| 🖻 🃁 Serial_Port1 | 📃 🧔 DAC      |         | Test Group | 6     | 0                | 0        |

| 🖮 🥼 Serial_Port2 | 🧧 🧔 Serial   | _Port1  | Test Group | 2     | 0                | 0        |

|                  | 🧧 🧔 Serial   | _Port2  | Test Group | 2     | 0                | 0        |

|                  |              |         |            | _     |                  |          |

**Figure 12** Test groups and tests in the *Digital example.fdm* model

# **Exploring Tests**

Clicking on a test in the explorer pane and clicking the **Covered Functions** tab shows the function(s) used by the test.

| ests                                                              | Test - Int_RAM_       | Check_00              |                 |      |

|-------------------------------------------------------------------|-----------------------|-----------------------|-----------------|------|

| 📝 Tests                                                           | Name: Int RAM Che     | ok 00                 |                 |      |

| 🖻 📝 CPU_Verify                                                    | Covered Functions: 1  |                       |                 |      |

| 😑 🃁 CPU_Int_RAM                                                   |                       |                       |                 |      |

| 😑 🕜 Int_RAM_Check_00                                              | Test Covered Function | ons                   |                 |      |

| wP_Memory uP, Memor     wP_Memory uP, Memo     wP_Memory uP, Memo | Show: All function    | How do I add coverage |                 |      |

| 🗟 📝 Int_RAM_Check_AA                                              | Components            |                       | Functions       |      |

| 😥 🕜 Int_RAM_Check_FF                                              | Name (Compon          | Subcomponent Name     | Name (Function) | Used |

|                                                                   | uP                    | Lower_Bus             | uP->Lower_Bus   |      |

| ≝ ∲ Flash                                                         |                       | II.                   | uP<-Lower_Bus   |      |

|                                                                   | н                     | Upper_Bus             | uP->Upper_Bus   |      |

| 🗄 🎾 DAC<br>🕀 🃁 Serial_Port1                                       |                       |                       | uP<-Upper_Bus   |      |

| 🗄 🃁 Serial_Port2                                                  | II II                 | CPU                   | uP_CPU          |      |

|                                                                   | •                     | Memory                | uP_Memory       | ×    |

|                                                                   | "                     | Serial_Port1          | uP_Serial_Port1 |      |

|                                                                   | "                     | Serial_Port2          | uP_Serial_Port2 |      |

|                                                                   | EPROM_lower           | Lower_Bus             | EPROM_L->uP     |      |

| Components and Functions                                          | EPROM_upper           | Upper_Bus             | EPROM_U->uP     |      |

| 7 Tests                                                           | RAM_lower             | Lower_Bus             | RAM_L->uP       |      |

| 10503                                                             |                       |                       | RAM_L<-uP       |      |

|                                                                   |                       |                       | RAM LI->uP      |      |

Figure 13 Test details for the Int\_RAM\_Check\_00 test

# **Creating a Model Report**

As with the Components and Functions view, from the Tests view, you can click the **Create Model Report** button on the toolbar to create an HTML report for the model. Refer to the Fault Detective online help for details regarding this report.

# **The Predicted Performance View**

🖎 Predicted Performance 🚽

Click the **Predicted Performance** button on the bottom left side of the screen to open the Predicted Performance view. This view allows you to create a test strategy, run the analysis, and create an analysis report.

The test strategy is listed in the left explorer pane. Details for the test strategy are shown in the detail pane. The Task Guide shows test analysis-related actions and shortcuts to supporting information.

The test strategy consists of a set of selected tests and a set of selected components. You select these elements from lists of all the tests and components in the model. By default, when you create or import a new model, there is one test strategy consisting of all the tests and components in the model.

You can analyze the test strategy by clicking the **Analyze** button in the toolbar or from a link in the Task Guide. The analysis creates predicted performance data consisting of:

- Predicted performance of the test strategy

- Predicted performance of individual faults

- Predicted performance of individual tests

- Suggestions for additional tests

When Fault Detective analyzes the test strategy, only the selected tests and components are considered in the analysis results. Therefore, the predicted performance displayed for the test strategy predicts what would result from running only the selected tests, on a device under test that consists of only the selected components. Tests and components that are not selected are not used in the analysis.

## **Creating a Predicted Performance Report**

Click the **Create Predicted Performance Report** button on the toolbar to create an HTML report for the selected test strategy. Refer to the Fault Detective online help for details regarding this report.

| Agilent Fault Detective - Digital<br>File Edit View Go Tools Actions He |                                                                                                        |                             |                           |                                   |                             |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------|-----------------------------------|-----------------------------|

|                                                                         | ·                                                                                                      |                             |                           |                                   |                             |

| 🔊 New 🔻 🚵 ד 📓 🎽 🐁 🐚 I                                                   | 14月 × 14 平                                                                                             |                             |                           |                                   |                             |

| 🕨 Analyze 📗 Coverage Table 🛛 🔂 C                                        | reate Predicted Performance Report                                                                     |                             |                           |                                   |                             |

| Predicted Performance                                                   | Summary                                                                                                |                             |                           |                                   |                             |

| 🔊 Favorite Test Strategy Files                                          |                                                                                                        |                             |                           |                                   | What do these numbers mean? |

| 🔄 🔬 Base Syndrome                                                       | Fault Analysis Summary:                                                                                |                             |                           |                                   |                             |

| - 🖩 Summary                                                             |                                                                                                        | Detection                   | Isolation                 | Repair                            |                             |

| - 🔝 Fault Analysis                                                      | Predicted Performance                                                                                  | 88.3 %                      | 98.0 %                    | 1.0                               |                             |

| - 🔲 Test Performance Analy                                              | Target                                                                                                 | 85.0 %                      | 85.0 %                    | 2.0                               |                             |

| 🦾 📗 Test Suggestion Analysi                                             | Delta                                                                                                  | 3.3 %                       | 13.0 %                    | -1.0                              |                             |

|                                                                         | Test Performance Summary:<br>Average Performance<br>Std. Dev. Performance<br>Test Suggestions Summary: | Detection<br>9.9 %<br>8.2 % | Unique Deta<br><1%<br><1% | ect Isolation<br>75.5 %<br>24.3 % |                             |

|                                                                         |                                                                                                        | Detection                   | Isolation                 | -                                 |                             |

|                                                                         | Maximum Improvement                                                                                    | 5.4 %                       | 1.9 %                     | -                                 |                             |

|                                                                         | Average Improvement per Suggestion                                                                     | 2.3 %                       | <1%                       | -                                 |                             |

| 🖙 Components and Functions                                              | Total Improvement                                                                                      | 11.4 %                      | 1.9 %                     |                                   |                             |

| Tests                                                                   | Options:                                                                                               |                             |                           |                                   |                             |

| Predicted Performance                                                   | <ul> <li>Maximum number of components in a fa<br/>Number of simulation runs per fault:</li> </ul>      | ult: 1<br>500               |                           |                                   |                             |

| 🝰 Suspect Faults                                                        | Simulation seed number:                                                                                | Auto G                      | ienerate                  |                                   |                             |

| *                                                                       | Analysis resolution:                                                                                   | Compo                       | nent                      |                                   |                             |

| Ready                                                                   |                                                                                                        |                             |                           |                                   |                             |

Figure 14 The Predicted Performance view

# **The Suspect Faults View**

🝰 Suspect Faults

Click the **Suspect Faults** button on the bottom left side of the screen to open the Suspect Faults view. This view is where you create, edit, save and load syndromes (a set of test results). Syndromes are listed in the explorer pane. Details for the selected syndrome are shown in the detail pane. The Task Guide shows syndrome-related actions and shortcuts to supporting information.

A syndrome is a set of unordered test results, with each test's result recorded as *Pass*, *Fail*, or *Skip*. Fault Detective stores syndromes in files with the extension *.tr*. You can create, edit, save and load syndromes in the Suspect Faults view.

Clicking the **Diagnose** button produces a list of suspect faults based on the pass, fail and skip information in the selected syndrome.

| Agilent Fault Detective - Digital example.fdm |               |                   |        |   |  |  |

|-----------------------------------------------|---------------|-------------------|--------|---|--|--|

| ile Edit View Go Tools Actions Help           |               |                   |        |   |  |  |

| 🖹 New 🝷 🔂 📲 💭 🐁 🗅 🛎 📆 🔀 🏛 Ŧ                   |               |                   |        |   |  |  |

| Diagnose Create Suspect Faults                |               |                   |        |   |  |  |

|                                               |               |                   |        |   |  |  |

| Suspect Faults                                | Syndrome -    | Base Syndron      | ne*    |   |  |  |

| Favorite Syndrome Files                       | Name: Base S  | yndrome           |        |   |  |  |

| 🖃 📑 Base Syndrome*                            |               | ,                 |        |   |  |  |

| 🦾 🚅 Suspect Faults                            | Group         | Name              | Result |   |  |  |

|                                               | <none></none> | CPU_Verify        | Pass   |   |  |  |

|                                               | CPU_Int_RAM   | Int_RAM_Check_00  | Pass   |   |  |  |

|                                               | "             | Int_RAM_Check_55  | Pass   |   |  |  |

|                                               | "             | Int_RAM_Check_AA  | Pass   |   |  |  |

|                                               | u             | Int_RAM_Check_FF  | Pass   |   |  |  |

|                                               | EPROM         | Lower_Read        | Fail   | _ |  |  |

|                                               | n             | Upper_Read        | Fail   |   |  |  |

|                                               | "             | Word_Read         | Fail   |   |  |  |

|                                               | RAM           | Lower_Read        | Pass   |   |  |  |

|                                               | u             | Upper_Read        | Pass   |   |  |  |

|                                               | u             | Word_Read         | Pass   |   |  |  |

|                                               | u             | Lower_Write       | Pass   |   |  |  |

|                                               | RAM           | Upper_Write       | Pass   |   |  |  |

| Components and Functions                      | n             | Word_Write        | Pass   |   |  |  |

|                                               | Flash         | Lower_Read        | Skip   |   |  |  |

| 🕜 Tests                                       | "             | Upper_Read        | Skip   |   |  |  |

| Predicted Performance                         | и<br>         | Word_Read         | Pass   |   |  |  |

| P c                                           | 11<br>11      | Lower_Write       | Pass   |   |  |  |

| 🖨 Suspect Faults                              | 11            | Honer Write<br>30 | Dace   | · |  |  |

| »<br>*                                        |               | , 30              |        |   |  |  |

| eady                                          |               |                   |        |   |  |  |

Figure 15 Syndrome details include the test groups, test names and test results (Pass, Fail or Skip)

# **Diagnosing a Syndrome**

Diagnosing a syndrome is the process whereby Fault Detective detects and isolates faults to determine the most likely cause of a failing test suite. You can diagnose a syndrome by clicking the **Diagnose** button on the toolbar or from a link in the Task Guide. Syndromes are critical data for Fault Detective's diagnosis and analysis processes. The diagnosis process uses a single syndrome that you specify in the Suspect Faults view. From the test results in this syndrome, Fault Detective produces a list of suspect faults in order of their likelihood. Clicking **Suspect Faults** under a syndrome in the explorer pane shows an ordered list of suspect faults in the detail pane.

| Agilent Fault Detective - Digital       File     Edit       View     Go       Tools     Actions       New $\bigcirc$ | tep<br>●■×±∓                                                                                  |                                                      |

|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------|

| 🕨 Diagnose 🛛 🗟 Create Suspect Faults                                                                                 | Report                                                                                        |                                                      |

| Suspect Faults                                                                                                       | Suspect Faults                                                                                |                                                      |

| <ul> <li>Favorite Syndrome Files</li> <li>Base Syndrome*</li> </ul>                                                  |                                                                                               | What is a score and how do I change it?              |

| Suspect Faults                                                                                                       | Score Sch Fault                                                                               | Detail                                               |

|                                                                                                                      | ▶ 98.9 U2 + U3 EPROM_lower                                                                    | EPROM_lower,Lower_Bus + EPROM_upper,Upper_Bus        |

|                                                                                                                      | 1.1 U1 uP                                                                                     | uP,Lower_Bus + uP,Upper_Bus + PF:uP\Lower_Bus\uP<-Lo |

| Components and Functions                                                                                             |                                                                                               |                                                      |

| 🕜 Tests                                                                                                              | <                                                                                             |                                                      |

| 🗠 Predicted Performance                                                                                              |                                                                                               | <u>.</u>                                             |

| Suspect Faults                                                                                                       | Scoring Algorithm:<br>Maximum number of subcomponents in a faul<br>Diagnosis Timeout (hh:mm): | TieBreaker1<br>: 7<br>00:01                          |

| Ready                                                                                                                |                                                                                               |                                                      |

Figure 16 Suspect faults in order of likelihood for *Digital example Default Syndrome*

## **Creating a Suspect Faults Report**

Click the **Create Suspect Faults Report** button on the toolbar or at the bottom of the suspect faults detail pane to create an HTML report for the selected syndrome. Refer to the Fault Detective online help for details regarding this report.

Agilent W1160C Fault Detective Getting Started Guide

3

# **Digital Modeling Tutorial**

About This Tutorial... 40 Step 1. Create, Save, Close, and Re-Open the Model 42 Step 2. Add a Component 43 Step 3. Add More Components 46 Step 4. Add Subcomponents 49 Step 5. Add Bus Subcomponents 52 Step 6. Add Functions 55 Step 7. Begin Modeling Tests 59 Step 8. Add Coverage 63 Step 9. Verify the Model 65 Step 10. Use Predicted Performance to Improve the Model 69 Step 11. Add More Tests and Coverage 73 Step 12. Iteratively Improve the Model 76 Step 13. Create Reports 78 Where To Go Next 79

This chapter contains a step-by-step tutorial that shows you how to model a digital DUT (Device Under Test). Although the model is for a digital DUT, the tutorial describes basic modeling techniques that apply to both digital and analog DUTs. You should perform this tutorial even if you plan to model analog DUTs. If you are modeling an analog DUT, refer to Chapter 7 for modeling information specific to analog DUTs after completing this tutorial.

## **About This Tutorial...**

The tutorial on the following pages takes about an hour to complete and shows how to model a Device Under Test (DUT) containing mostly digital components. The tutorial uses the *Digital example.fdm* model. This model file is located in:

<drive>:\Program Files\Agilent\Fault Detective\Fault

Detective 4.7\Samples\Models\Digital

Model files for completed tutorial steps are located in:

<drive>:\Program Files\Agilent\Fault Detective\Fault

Detective 4.7\Samples\Models\Tutorial

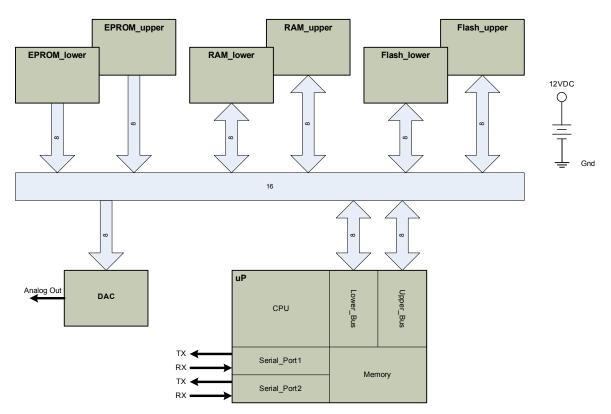

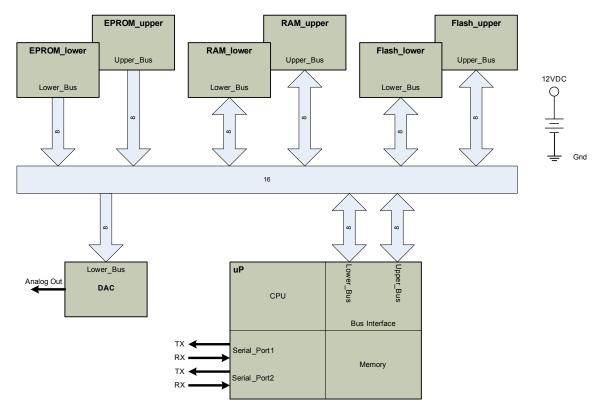

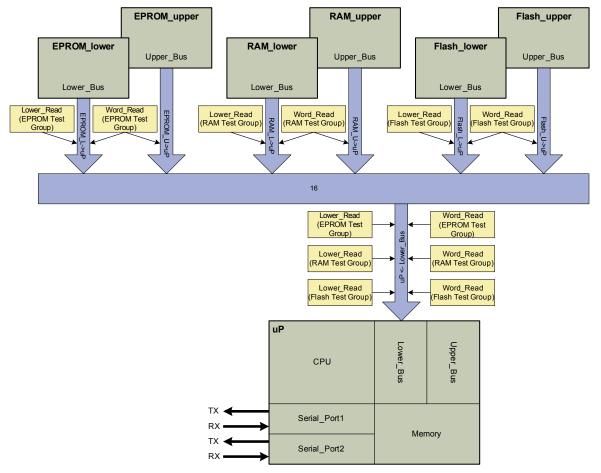

As shown in Figure 17, the DUT contains a microprocessor, a data bus, EPROMs, RAM, Flash, a DAC and a power supply.

Figure 17 Block diagram of the DUT used in *Digital example.fdm*

Tip Notice that we are using a block diagram—not a schematic. Modeling is done at a functional test level which usually best correlates to a block diagram. If a block diagram does not exist, you can use a schematic. However, schematics typically have a large number of low-level parts such as resistors, capacitors and inductors. In most cases, these low-level parts are not tested directly by the functional tests and should not be part of the Fault Detective model.

## Step 1. Create, Save, Close, and Re-Open the Model

- 1 To open the Fault Detective application, click Start > All Programs > Agilent Fault Detective > Fault Detective 4.7 > Fault Detective 4.7.

- 2 Create a new model. Click File > New > Model.

- **3** Save and name the model. Click **File > Save As...** and navigate to:

<drive>:\Program Files\Agilent\Fault Detective\Fault

Detective 4.7\Samples\Models\Tutorial

Enter the file name *tutorial\_step1.fdm* and click **Save**.

- 4 Close the model. Click File > Close All.

- Tip Clicking Close All closes and saves the model file (*.fdm*), syndrome files (*.tr*), and test strategy files (*.ts*). The model file holds the components, subcomponents, functions and tests for your model. The syndrome and test strategy files are discussed later in this manual; you will notice that Fault Detective creates a folder (in this case, tutorial step1 files) to hold these files.

5 Click File > Open > Model. Navigate to the saved tutorial\_step1.fdm file and click Open to open the model.

## Step 2. Add a Component

In Fault Detective, a component represents the functionality provided by the DUT's physical parts. In our model, components are the high-level circuit elements shown in the block diagram. These are the microprocessor, EPROMs, RAM, Flash, DAC, and power supply.

1 With the *tutorial\_step1.fdm* model open, click the **Components and Functions** button

- **2** Click the add component button **in the task toolbar**.

- **3** In the explorer pane, type over *NewComponent* with the name *uP*.

- **4** Enter the following component information (this information is optional but it is good practice to enter):

- Schematic Reference: U1

- Part Number: 68MC302

- Diagnostic Comment: Microprocessor

- Notes: This is a very fast, low-power, 16-bit microprocessor.

It has 32MBytes of internal RAM.

It also has two serial ports.

For this model, leave the Relative Failure Rate set to Medium (the default) for this component, and all components. The Relative Failure Rate can be important in modeling. Refer to the Fault Detective online help for more information (search for *relative failure rate*).

Similarly, leave the Component Cost set to its default, 0.00, for the purposes of this tutorial. You can use the Component Cost to help you determine the repair order of suspect faults. Search for *component cost* in the online help for more information.

5 When finished entering the information, click on the component name (uP) in the explorer pane (left pane). By moving focus from the detail pane to the explorer pane, you are indicating to Fault Detective that you are done entering the information for this component.

- Notice that a default function (*NewFunction*) is automatically created for each component. Ignore these default functions for now. You will learn more about functions in "Step 6. Add Functions".

- 6 Save and name the model. Click File > Save As..., enter the file name *tutorial\_step2.fdm* and click Save.

- Tips Instead of using buttons in the task bar, you can add model elements by right-clicking from anywhere in the explorer pane.

- The Task Guide supplements this tutorial and provides how-to information and links to additional help topics relating to the particular view. Keep the Task Guide open (click View > Task Guide) while doing this tutorial.

Figure 18 The Task Guide supplements this tutorial

## Step 3. Add More Components

When modeling, keep in mind that a component is a *replaceable* part or group of parts. A component will often equate to an integrated circuit such as the microprocessor, EPROM, or DAC. Often, a component consists of a group of parts that are replaced as an assembly—a power supply, for example. You will learn more about making decisions regarding components as we work through the tutorial.

1 With the *tutorial\_step2.fdm* model open, click the

add component button

- **2** In the explorer pane, type over *NewComponent* with the name *EPROM\_lower*. Add the additional information for this component from the table below.

- **3** Continue adding the remaining components shown in Table 1. Figure 19 shows the explorer pane with all components added.

After you have added a few components from Table 1, you can close the model and open *tutorial\_step3.fdm* in this directory path:

<drive>:\Program Files\Agilent\Fault Detective\Fault Detective 4.7\

Samples\Models\Tutorial

This model file has all the components added for you.

#### Table 1 Components for the Digital Example

| Name<br>(no spaces in name) | Schematic<br>Reference | Part Number | Diagnostic Comment |

|-----------------------------|------------------------|-------------|--------------------|

| uP                          | U1                     | 68MC302     | Microprocessor     |

| EPROM_lower                 | U2                     | EP-512      | EPROM, lower       |

| EPROM_upper                 | U3                     | EP-512      | EPROM, upper       |

| RAM_lower                   | U4                     | DDR2-512    | RAM, lower         |

| Name<br>(no spaces in name) | Schematic<br>Reference | Part Number | Diagnostic Comment                         |

|-----------------------------|------------------------|-------------|--------------------------------------------|

| RAM_upper                   | U5                     | DDR2-512    | RAM, upper                                 |

| Flash_lower                 | U6                     | 28F512      | Flash, lower                               |

| Flash_upper                 | U7                     | 28F512      | Flash, upper                               |

| DAC                         | U8                     | DAC8        | 8-bit Digital-to-Analog Converter (DAC)    |

| 12VDC                       | PS2                    | PS-12VDC    | +12 VDC power supply for Flash programming |

Table 1

Components for the Digital Example (continued)

| Components and Functions | Compoi         |

|--------------------------|----------------|

| Components and Functions | Component      |

|                          | Nam            |

| 😥 🛲 EPROM_lower U2       | 🕨 🛲 🛛 uP 👔     |

| 🔄 🛲 EPROM_upper U3       | EPR            |

| 🔃 🛲 RAM_lower U4         | 📕 🛲 EF         |

| 😟 🛲 RAM_upper_U5         |                |

| 庄 🛲 Flash_lower U6       | - <del>-</del> |

| 庄 🛲 Flash_upper U7       | - <del>-</del> |

| 庄 🛲 DAC U8               |                |

| 庄 🛲 12VDC PS2            |                |

|                          |                |

|                          |                |

Figure 19 Explorer pane showing components

#### Tips Modeling Components

- The goal when modeling components is to model the relationship between the tests and the DUT by modeling components whose functionality is actually being used in the functional tests.

- To identify components to be modeled, start by going through your tests one by one, asking the question, "Which components must operate to some degree for this test to pass?"

- When choosing components, select those that must be at least partially functional for the tests to

pass. Do not model components that cannot cause functional test failures. Typically, a DUT made

up of hundreds of parts can be represented by a model with tens of components.

#### **The Notes: Field**

You can enter supporting details in the Notes: field or add links to supporting documentation, such as HTML files and URLs. This allows you to provide a transfer of knowledge from the model designer to the production floor. When necessary, test personnel can locate supporting documents such as schematics, block diagrams or parts cost information. The Notes: field is available for components, functions and tests.

#### **Adding Model Elements**

This tutorial uses buttons in the task toolbar to add model elements. You can also add model elements from the Task Guide or by right-clicking from anywhere in the explorer pane.

#### **Moving Model Elements in the Explorer Pane**

You can drag and drop model elements in the explorer pane or you can use the move up  $|^{2}$

and

move down 😨 buttons in the toolbar to arrange model elements.

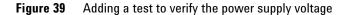

## **Step 4. Add Subcomponents**